Descrição

Características Técnicas

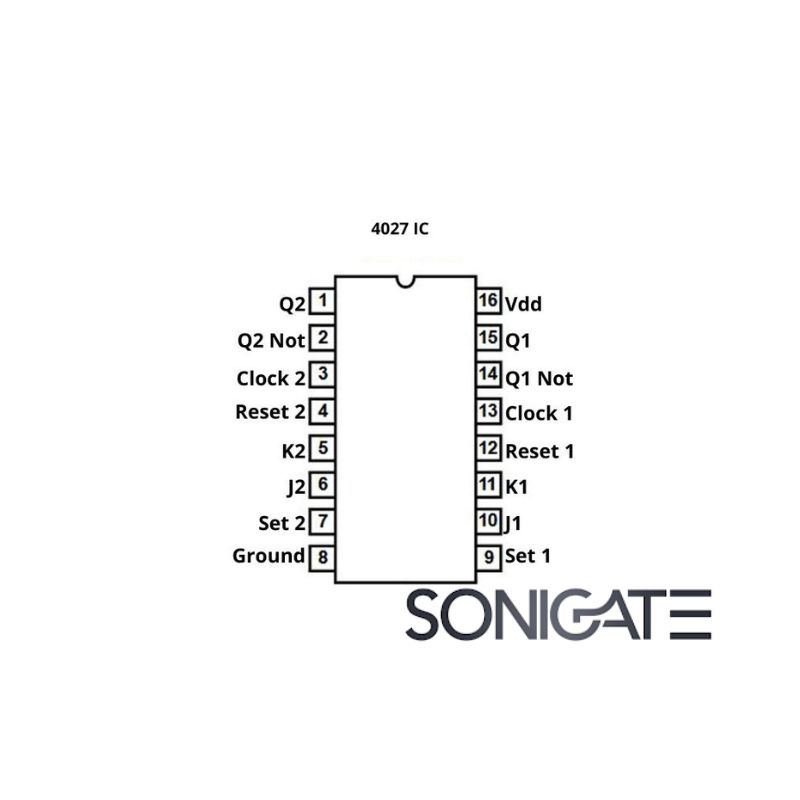

Família lógica: CMOS série 4000

Função: 2 flip-flops tipo JK independentes

Entradas por flip-flop:

J e K

Clock (borda de subida)

Set assíncrono

Reset assíncrono

Saídas: Q e Q̅

Tensão de alimentação (Vdd): 3 V a 15 V

Consumo energético: muito baixo

Elevada imunidade ao ruído

Frequência máxima de clock típica: ≈ 3 MHz (dependente de Vdd)

Encapsulamento comum: DIP-16

Intervalo de temperatura de operação: –40°C a +85°C

Principais Aplicações

Contadores digitais e divisores de frequência

Lógica sequencial e circuitos de memória

Sistemas de temporização e controlo

Geração de sinais de relógio e toggling

Equipamentos eletrónicos de baixo consumo

Projetos educativos de eletrónica digital

Vantagens

Dois flip-flops JK num único encapsulamento

Entradas Set e Reset assíncronas aumentam a flexibilidade

Opera numa ampla gama de tensões

Consumo energético extremamente reduzido

Elevada estabilidade e imunidade ao ruído

Fácil integração em sistemas digitais CMOS